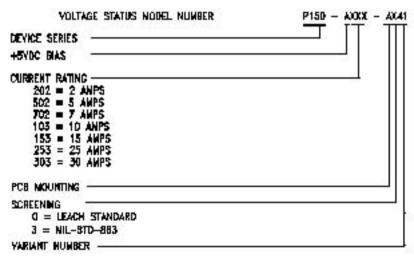

# P150 SERIES

### **ENGINEERING DATA SHEET**

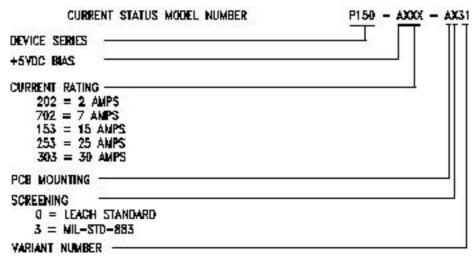

SOLID STATE POWER CONTROLLER 28 VDC, 1PNO-WITH CURRENT OR VOLTAGE STATUS OUTPUT UP TO 30 AMP RATING

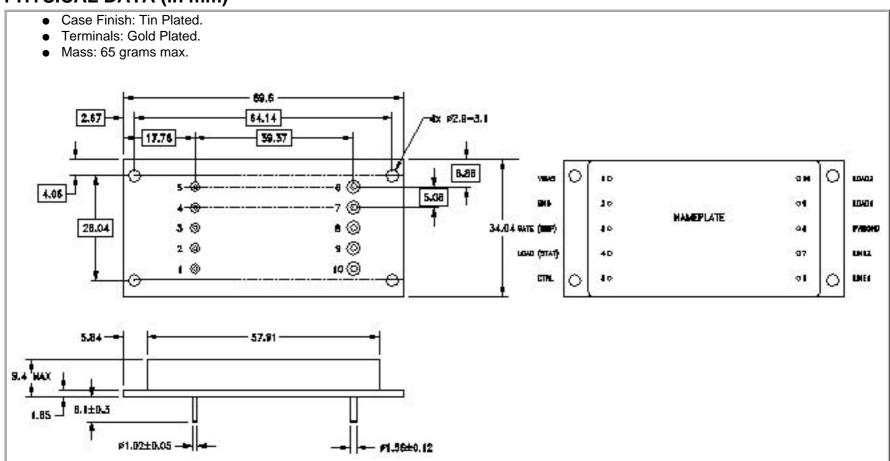

SIZE: 69.6 x 34 x 9.65 mm

#### **DESCRIPTION**

The P150 Series of Solid State Power Controllers (SSPC) is rated from 2 to 30 Amperes. These LEACH SSPC's feature reliable, trouble free switching together with real short circuit protection. Employing a power FET output stage, and built using thick film technology, they offer low on state resistance and low on state voltage drop. They react to fault condition and can shutdown within microseconds, if required. Two status signals, derived from the load current value or voltage and from the device gate, are reported via optical isolators. Designed to operate in 28 VDC systems, these devices do not require derating for any load type. They are hermetically sealed, in a metal package.

#### **FEATURES**

.Fast acting

Built-in overload and short circuit protection

Load current or voltage status

.FET Gate status or trip status

Very low voltage drop

No derating up to 105° C

.Trip free

Fully isolated bias, control and status No derating for non-resistive loads Exceeds MIL-P-81653C requirements Very low voltage drop output stage

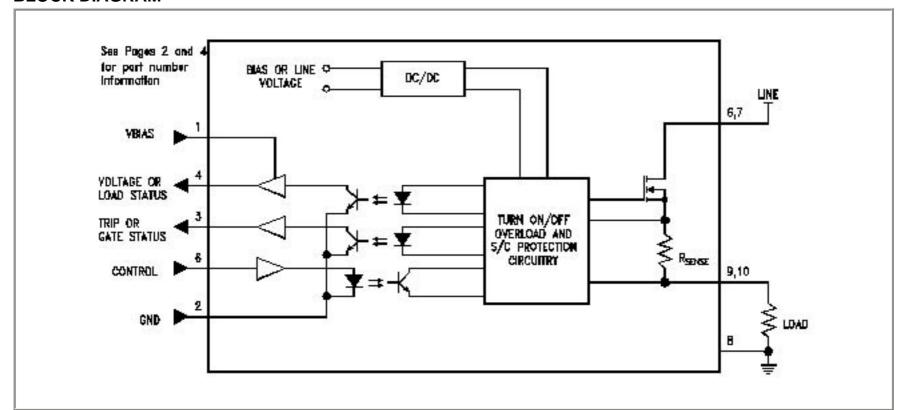

### **BLOCK DIAGRAM**

Featuring LEACH® power and control solutions www.esterline.com

P.O. Box 5032 Buena Park, CA 90622

57430 Sarralbe France

**ASIA**

Units 602-603 6/F Lakeside 1 No.8 Science Park West Avenue Phase Two, Hong Kong Science Park Pak Shek Kok, Tai Po, N.T.

Hong Kong

Tel: (33) 3 87 97 31 01 Tel: (852) 2 191 3830 Tel: (01) 714-736-7599 Fax: (01) 714-670-1145 Fax: (33) 3 87 97 96 86 Fax: (852) 2 389 5803

Data sheets are for initial product selection and comparison. Contact Esterline Power Systems prior to choosing a component.

Date of issue: 4/06 - 15 -Page 1 of 6

### **ELECTRICAL CHARACTERISTICS (CURRENT STATUS)**

#### P150 SERIES

| Typical values are at 25 ± 5° C INPUT | DEVICE WITH CURRENT STATUS |      |      |      |      |       |

|---------------------------------------|----------------------------|------|------|------|------|-------|

| Parameter                             | Symbol                     | Min. | Тур. | Max. | Unit | Notes |

| BIAS On Voltage                       | V <sub>IHB</sub>           | 4.5  |      | 5.5  | V    | 1,2   |

| BIAS On current                       | I <sub>IHB</sub>           |      |      | 10   | mA   | 3     |

| BIAS Off current                      | I <sub>ILB</sub>           |      |      | 1    | mA   | 3     |

| CONTROL voltage on                    | V <sub>IHC</sub>           | 2.4  |      |      | V    |       |

| CONTROL voltage off                   | V <sub>ILC</sub>           | -0.8 |      | 0.8  | V    |       |

| CONTROL current on                    | I <sub>IHC</sub>           |      |      | 50   | μA   | 4     |

| CONTROL current off                   | l <sub>ILC</sub>           |      |      | -10  | μA   | 5     |

| Transients (BIAS input)               | V <sub>TB</sub>            |      |      | +50  | V    | 6     |

Notes:

- 1. BIAS voltage must be a step function.

- 2. No reverse polarity protection.

- 3. BIAS voltage is 5.0 V.

- 4. Control voltage at 2.4 vdc.

- 5. Control voltage at 0.4 vdc.

- 6. Max. Duration 50 ms, Duty Cycle 1%, Repetition Rate 1 Hz.

| 5. BIAG voltage is 5.0 v. |                   |      |      | ., , . , |          |      |

|---------------------------|-------------------|------|------|----------|----------|------|

| OUTPUT                    |                   |      |      |          |          |      |

| Parameter                 | Symbol            | Min. | Тур. | Max.     | Unit     | Note |

| Load current              | I <sub>L</sub>    | 0    |      | 100      | %I rated | 1    |

| On state voltage drop     | V <sub>LD</sub>   |      |      | 200      | mV       | 2    |

| Off state line voltage    | V <sub>L</sub>    |      |      | 32       | V        | 3    |

| Gate high voltage         | V <sub>OHS</sub>  | 2.4  |      |          | V        |      |

| Gate high current         | I <sub>OHS</sub>  |      |      | 50       | μΑ       |      |

| Gate low voltage          | V <sub>OLS</sub>  |      |      | 0.8      | V        |      |

| Gate low current          | lols              |      |      | 0.2      | mA       |      |

| Load pick up              | I <sub>SON</sub>  |      |      | 15       | %I rated |      |

| Load drop out             | I <sub>SOFF</sub> | 5    |      |          | %I rated |      |

| Leakage current           | ارر               |      |      | 1        | mA       | 4    |

| Transient voltage         | V <sub>T</sub>    |      |      | +50      | V        | 5    |

| Spikes                    | V <sub>S</sub>    | -600 |      | +600     | V        | 6    |

| Trip current              | I <sub>TR</sub>   | 110  | 130  | 145      | %I rated | 7    |

| solation voltage          | V <sub>ISO</sub>  |      |      | 750      | VRMS     |      |

| Insulation resistance     | R <sub>INS</sub>  | 100  |      | 1000     | ΜΩ       | 8    |

- 1. Load current is subject to thermal derating.

- 2. At load current  $I_L$ =100% rated value.

- 3. Reverse polarity is not blocked and may damage the SSPC.

- 4. At  $V_L$ =28V, Case temperature = 105° C.

- 5. Duration 12.5 ms max. per MII-STD-704D.

- 6. Duration 10 µs max. per Mil-STD-704D.

- 7. See Trip Characteristics.

- 8. 500 Vdc, ± 10%

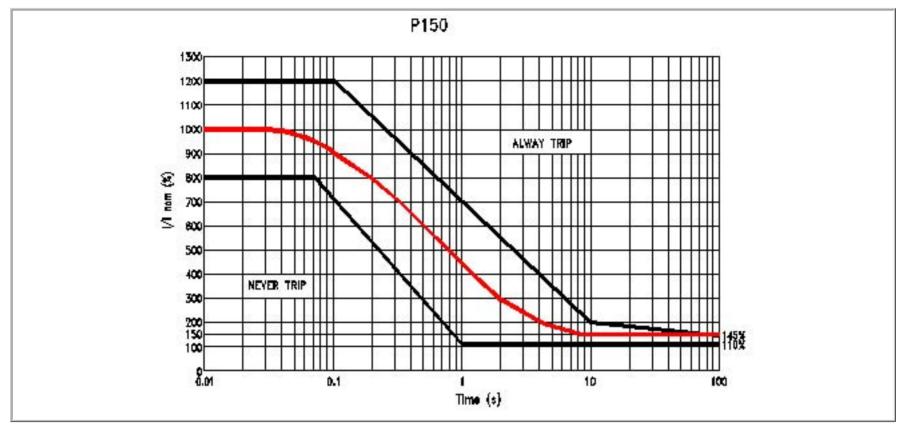

TRIP CHARACTERISTIC P150 SERIES

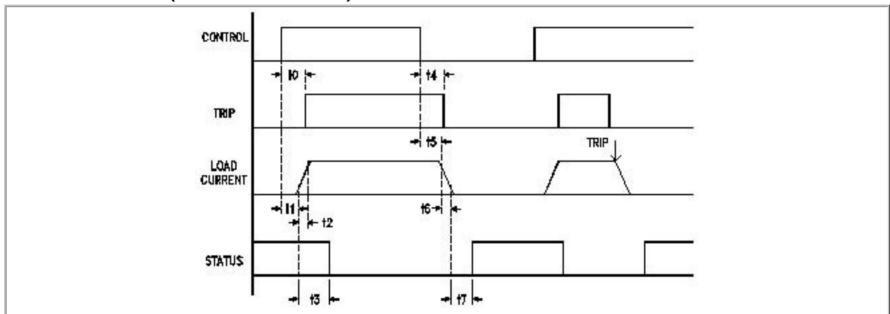

## **TIMING DIAGRAM (CURRENT STATUS)**

#### **TIMING**

| Parameter              | Symbol         | Тур. | Max. | Unit | Note |

|------------------------|----------------|------|------|------|------|

| CONTROL to GATE delay  | t <sub>0</sub> | 300  | 1000 | μs   |      |

| Turn on delay          | t <sub>1</sub> | 150  | 200  | μs   |      |

| Load current rise time | t <sub>2</sub> | 30   | 1000 | μs   |      |

| Turn on to LOAD delay  | t <sub>3</sub> | 75   | 1000 | μs   |      |

| CONTROL to GATE        | t <sub>4</sub> | 150  | 1000 | μs   |      |

| Turn off delay         | t <sub>5</sub> | 150  | 200  | μs   |      |

| Load current fall time | t <sub>6</sub> | 20   | 1000 | μs   | 2    |

| Turn off to LOAD delay | t <sub>7</sub> | 400  | 1000 | μs   |      |

- 1. All timing measurements taken at 10% and 90% points into resistive rated load.

- 2. Current fall time from trip dependant on overload condition.

### **ELECTRICAL CHARACTERISTICS (VOLTAGE STATUS)**

#### P150 SERIES

| Typical values are at 25 ± 5° C     | are at 25 ± 5° DEVICE WITH VOLTAGE STATUS LIMITS |                                                                        | UNIT | NOTES |                 |       |

|-------------------------------------|--------------------------------------------------|------------------------------------------------------------------------|------|-------|-----------------|-------|

| INPUT                               |                                                  |                                                                        |      |       |                 |       |

| Parameter                           | Symbol                                           | CONDITIONS<br>-55°C to +105°C (1)                                      | MIN  | MAX   |                 |       |

| Logic supply voltage                | V <sub>CC</sub>                                  |                                                                        | 4.5  | 5.5   | Vdc             |       |

| CONTROL voltage high                | V <sub>IH</sub>                                  |                                                                        | 2.0  |       | Vdc             |       |

| CONTROL voltage low                 | V <sub>IL</sub>                                  |                                                                        |      | 0.8   | Vdc             |       |

| Transient                           |                                                  | Pulse width = 12.5 msec max. per MIL-STD-704D                          |      | +50   | Vdc             | 2     |

| Spikes                              |                                                  | Pulse width = 10 μsec max. per MIL-STD-704D                            | -600 | +600  | Vdc             | 2     |

| REQUIREMENTS                        | ,                                                |                                                                        | ,    | ,     | ,               |       |

| 28 Vdc initialization spike voltage |                                                  | During of output spike at 50% amplitude shall be 100µsec maximum       |      | 5     | V <sub>PR</sub> |       |

| 5 Vdc initialization control        |                                                  | Vline = 28 Vdc, Vcontrol = 0 Vdc, Vbias = 0 to 5 Vdc, rated at <1 msec |      |       |                 | 3     |

| Logic supply current                | I <sub>CC</sub>                                  | V <sub>CC</sub> =5.5 Vdc                                               |      | 50    | mA              | 4     |

| Load current continuous             | I <sub>LOAD</sub>                                |                                                                        |      | 100   | %l              |       |

| "ON" state voltage drop             | Vo                                               |                                                                        |      | 200   | mV              | 5     |

| Leakage current                     | IL                                               |                                                                        |      | 1     | mA              |       |

| STATUS & TRIP voltage high          | V <sub>OH</sub>                                  | IOH=5mA                                                                | 2.4  |       | Vdc             |       |

| STATUS & TRIP voltage low           | V <sub>OL</sub>                                  | IOL=1mA                                                                |      | 0.4   | Vdc             |       |

| CONTROL current high                | I <sub>IH</sub>                                  | VI=2.4 Vdc                                                             |      | 50    | μA              |       |

| CONTROL current low                 | I <sub>IL</sub>                                  | VI=0.4 Vdc                                                             |      | 10    | μA              |       |

| Output "ON" sense voltage           | V <sub>ON</sub>                                  | See Timing Diagram (Voltage Status)                                    | 30   | 70    | %               | 5,6,7 |

- 1. Unless specified otherwise, test conditions shall be at Vcc= $5.0\pm0.25$ Vdc and Vline= $28\pm0.5$ Vdc. The design shall be capable of meeting all requirements with Vcc=4.5 to 5.5Vdc.

- 2. The transient and spike requirements apply only to the 28Vdc power lines.

- 3. The device output shall remain off when 5V bias is raised from 0 to 5Vdc.

- 4. Without any load connected to the STATUS or TRIP outputs.

- 5. At 100% rated current.

- 6. Rated resistive load; measurements taken between 10% and 90% points.

- 7. Percent of actual applied Vline.

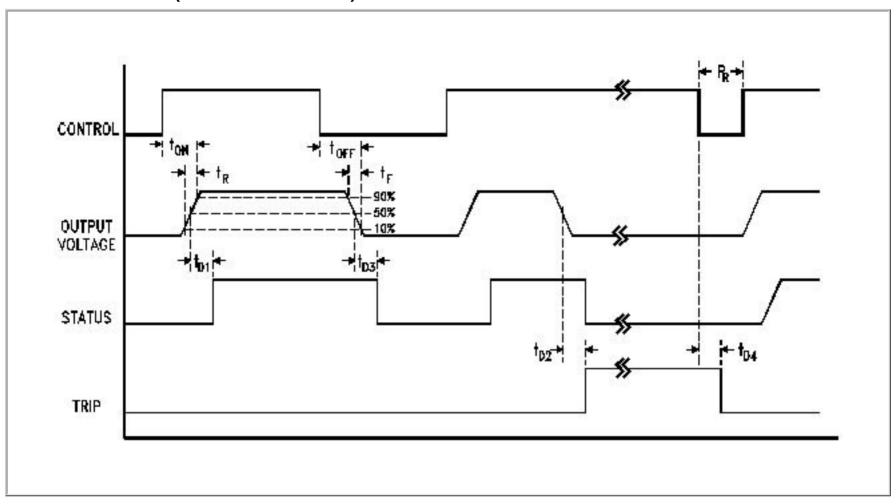

### **TIMING**

| Parameter                            | Symbol           | Conditions -55°C to +105°c | Min. | Max. | Unit | Notes |

|--------------------------------------|------------------|----------------------------|------|------|------|-------|

| Turn-on time                         | t <sub>on</sub>  |                            |      | 1000 | µsec | 1,3   |

| Turn-off time                        | t <sub>off</sub> |                            |      | 1000 | µsec | 1,3   |

| Load voltage rise time               | t <sub>R</sub>   |                            | 20   | 200  | µsec | 1,3   |

| Load voltage fall time               | t <sub>F</sub>   |                            |      | 200  | µsec | 1,3   |

| STATUS on delay                      | t <sub>D1</sub>  | See Timing Diagram         |      | 2000 | µsec | 1     |

| STATUS of delay                      | t <sub>D3</sub>  |                            |      | 2000 | µsec | 1     |

| TRIP on delay                        | t <sub>D2</sub>  |                            |      | 150  | µsec | 2     |

| TRIP of delay                        | t <sub>D4</sub>  |                            |      | 150  | µsec | 2     |

| CONTROL pulse width for device reset | P <sub>R</sub>   |                            | 50   |      | msec |       |

- 1. At 100% rated current.

- 2. At 250% rated current.

- 3. Rated resistive load; measurements taken between 10% and 90% points.

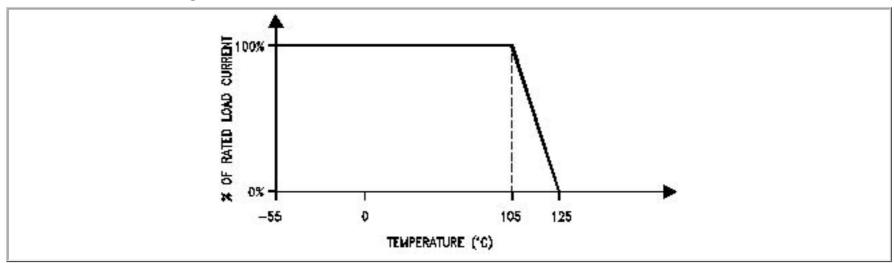

| Parameter                                   | Symbol              | Min. | Max.  | Unit  | Notes |

|---------------------------------------------|---------------------|------|-------|-------|-------|

| Operational Temp. Range                     | T <sub>op</sub>     | -55  | 125   | ° C   | 1,2   |

| Storage Temp. Range                         | T <sub>st</sub>     | -55  | 125   | ° C   |       |

| Thermal resistance junction to case $	heta$ | $\theta_{\sf jc}$   |      | 15    | ° C/W |       |

| Max. Junction Temperature of Output Stage   | T <sub>j(max)</sub> |      | 150   | ° C   |       |

| Vibration                                   |                     |      | 20    | G     | 3     |

| Acceleration                                |                     |      | 3000  | G     | 4     |

| Shock                                       |                     |      | 1500  | G     | 5     |

| Seal (Hermetic)                             |                     |      |       |       | 7     |

| Altitude                                    |                     |      | 80000 | ft    |       |

| MTBF                                        |                     |      | 1.1   | hours | 6     |

#### Notes:

- 1. Case temperature.

- 2. See thermal derating curve.

- 3. MIL-P-883C, Method 2007, test condition A; 20-2000 Hz.

- 4. MIL-P-883C, Method 2001, test condition A.

- 5. MIL-P-883C, Method 2002, test condition B, 0.5 ms.

- 6. Per MIL-HBK-217E, Quality level B-1, AUT environment at 25°C.

- 7. Meets the leakage levels in accordance with MIL-STD-883, Method 1014, test condition A1.

### THERMAL DERATING

### PHYSICAL DATA (in mm)

This engineering data sheet is designed for initial selection and comparison of products. While every effort is made to ensure the accuracy of all data, each part number, and its application, must be controlled by a Product Control Drawing (PCD). Please contact PowerCom, a Leach International Company, for further information.